晶圆级封装:适用于移动应用的有吸引力的封装解决方案

如今,许多电子系统仍然由多个元件组成,这些元件在晶片切割后单独封装,并且使用传统的印刷电路板互连。然而,这些年来,对于更“苛刻”的应用就需要先进的3D集成和互连技术。因为这大大减小了电子系统的尺寸,并且实现了子电路之间更快,更短的连接。这些💯技术之一是晶圆级封装(Wafer Level Packaging),即多个裸片在晶圆上同时被封装。由于整个晶圆现在是一次性封装,因此该解决方案比传统封装方案成本更低。此外,所得封装后芯片尺寸🌱更小,更薄,这是智能手机等尺寸敏感设备非常看重的。在现今的智能手机上,大概5/7的芯片是晶圆级封装的,而且数量还在不断增加。

扇入和扇出

有两种主要类型的晶圆级封装:扇入式和扇出式,它们的区别主要在重分布层中。重分布层(通常是有机层)用于将裸片的接口(I/ O)🐈重新布线到所需的(凸块)位置。扇入就是重分布层迹线向内布线,形成一个非常小的封装(大致对应于裸片本身的尺寸)。但是,重分布工艺还可以用于扩展封装的可用区域,延伸芯片触点到超出芯片尺寸就形成了扇出式封装。通常,这种扇出WLP(FO-WLP)技术提供比扇入式WLP技术更多的I /O数量。

在移动应用中,扇出晶圆级封装正在逐步取代更传统的封装上封装(PoP)存储器逻辑芯片堆叠解决方案。

这些PoP比扇出式厚得多,并且受到的互连带宽和密度以及有限的间距✤缩放(几百微米)的限制。在这些应用中,FO-WLP也优于其他可用的高带宽3D技术,例如3D堆叠(其中逻辑管芯中的热点可能影响存储器数据保持能力)或2.5D堆叠(🌳其中较长的互连线产生较高的互连功率和额外成本)。

两个基本的“扇出”流程

在过去几年中,已经涌现了各种FO-WLP方法,以满足对高数据速率和宽I/ O数量的日益增长的需求,并满足对封ꦺ装上增加的功能集成的需求。所有这ꦦ些方法都从两个基本的扇出流程中的一个开始:“mold first”或“redistribution layer first”。

在“mold first &lඣdquo;工艺中,首先将裸片组装在临时载体上,然后进行晶片包覆成型。环氧树脂的功能是保护各个组件并将它们粘在一起。在最后,制作重分部层并建立连接。在“redistribution layer first”工艺中,在重分布层的工艺之后ꩲ再做裸片组装和晶片注塑成型。

这些方法中的每一种都有其自身的一些缺点。例如,在“mold first “工艺中,裸片通常在注塑成型之后发生移位,这使得实现低于100μm的互连节距非常具有挑战性。&ldqu🔥o;redistribution layer first”工艺中,可实现的密度受到(有机)再分布层能够实现的线和空间分辨率的限制。

Fဣlip-chip on FO-WLP:一种新的“扇出”方法,可实现更高的互连密🔯度

为了满足更高密度,更高带宽的芯片到芯片连接的需求,IMEC团队在30꧙0mm晶圆上开发了一种新颖的FO-WLP方法,称为Flip-chip on FO-WLP。

这个工艺属于“mold first ”工艺,但与标准的“mold 🦄first ”ඣ工艺相反,芯片在包覆成型之前已经互相连接。

下面将解释这种方法的优点以及挑战。

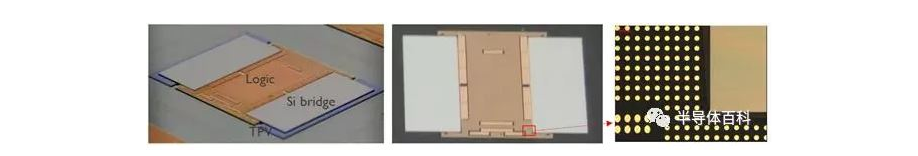

关键部件:through package vias(TPV)和硅桥

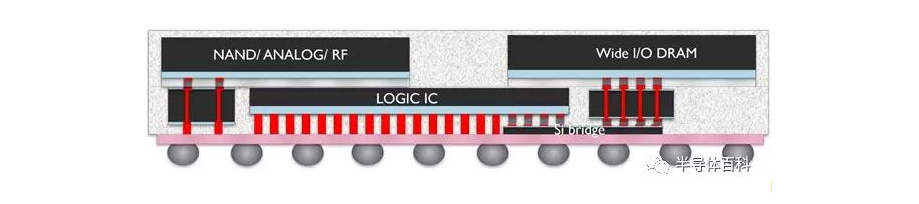

这种新的扇出方案的已经在TQV上得到验证。TQV由七个独立的芯片组件组成:Wide I / O DRAM,闪存,逻辑,两个TPV裸片和两个硅桥。因为这个TQV只是用🌄于验证。因此,逻辑和存储器芯片不是全功能的:它们是“模拟”裸片,用于测试凸点连接之间的电连续性。

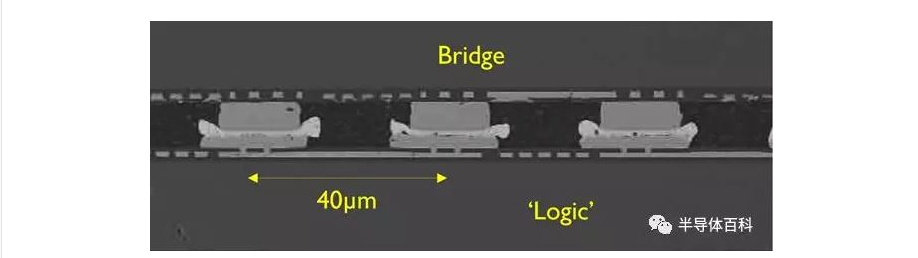

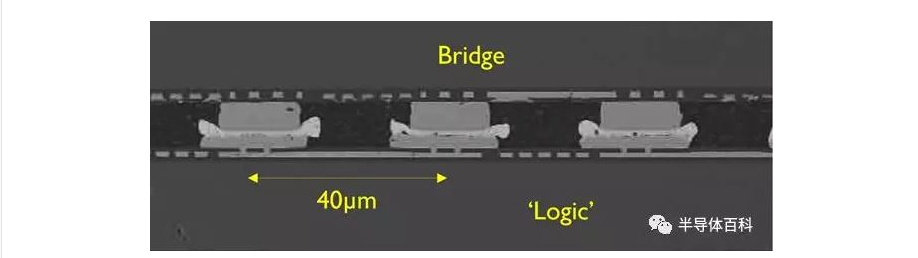

硅桥和TPV裸片是实现高密度连接的关键部件。TPV裸片具有硅通孔(TSV)和40μm节距的凸点。硅桥具有40μm和20μm节距的凸块。这些元件在功能芯片(例如逻辑和存储器芯片)之间形成桥接,实现具有20&mu💝;m凸块节距的超高芯片到芯片互连密度。

与标准“mold first “工艺相比,另一个关键工艺是裸片间的紧密对准。在该关键组装步骤中,需要将各个裸片高精度地放置并临时键合在平坦的硅晶圆上。

Flip-chip19081301.JPGFlip-chip on FO-WLP芯片概念图。

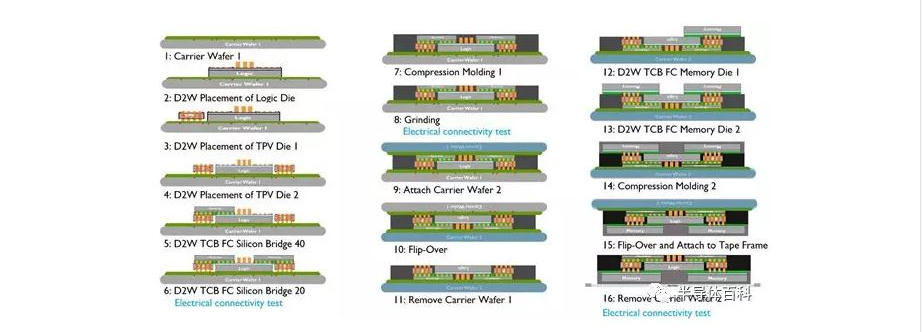

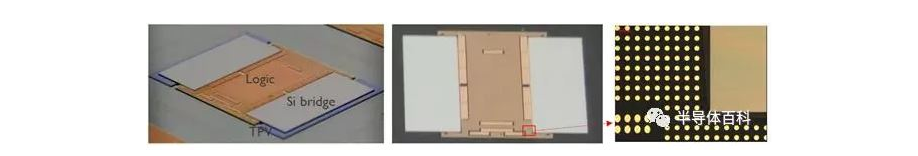

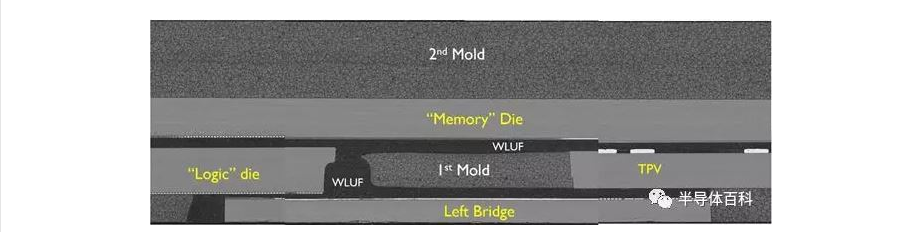

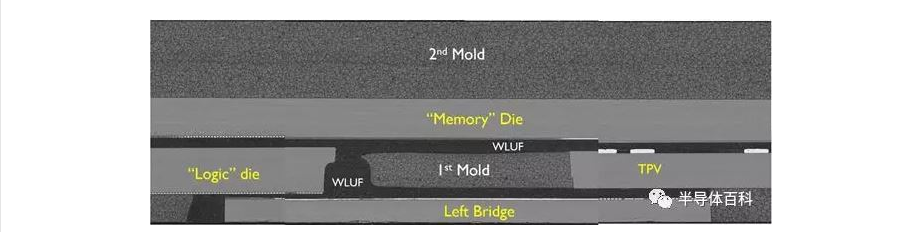

工艺流程细节

在组装工艺流程的第一步骤中,将TPV片和逻辑裸片放置在覆有临时键合层的载体晶片上。接下来,使用热压接合(TCB)工艺连接硅桥(具有40μm和20μm的凸块间距)与逻辑裸片和TPV裸片。在该工艺步骤中,具有40μm节距的凸块连接到逻辑裸片的左侧和TPV裸片。20μm间距凸块连接到逻辑裸片的右侧。在下一步骤中,晶片由液态化合物注塑成型。测试显示完全填充,甚至是硅桥下方区域。然后,通过研磨抛光暴露铜柱,以便稍后与重分布层连接。在将减薄的晶片翻转并第二载体键合,并移除第一载体。之后,使用倒装芯片技术组装存储器裸片。最后,再一次晶圆级注模和第二载体的移除完成工艺流程。在工艺步骤之间,会进行连续性测试以验证电路完整。最后得到封装厚度仅为300-400μm的芯片(不包括焊球)。

Flip-chip19081302.JPGFlip-chip on FO-WLP芯片:封装工艺流程

Flip-chip19081303.JPG图示了裸片放置和桥接之后的步骤5至8(左); 在注塑和背面研磨之后(中)和暴露的Cu柱在封装体表面上(右)

Flip-chip19081304.JPG最终的第二晶圆级成型之后的横截面

主要挑战和解决方案

这套♕工艺流程带来了一系列挑战,需要克服这𓆉些挑战才能确保具有超高芯片到芯片互连密度的全功能封装解决方案。

其中一个问题是在组装工艺流程中裸片可能倾斜,特别是对于长而窄的TPV裸片和硅桥。这些裸片的倾斜可能会破坏组件之间的互连。为了评估倾斜是否以及何时发生,IMEC团队采用不同的力量来放置TPV裸片。该团队观察到,即使是最大的贴装力,倾斜也限🦩制在5μm以下,这足够低以保持连接性。

接下来是,逻辑裸片和TPV裸片之间的对准,这已经引起了相🐭当大的关注,ꦉ并且被认为是FO-WLP工艺的关键因素。

逻辑裸片和TPV裸片彼此靠的非常近,并且需要精确的对准步骤以实现后续的硅桥40μm和20μm凸块节距堆叠。例如,为了实现所需的20μm凸块间距,仅可以容忍逻辑裸片和TPV裸片之间的最大+/-3🍸μm的对准误差。为了实现这种极小的误差,该团队将对准标记引入到载体和裸片设计中。逻辑裸片首先与载体😼对准。接下来,放置TPV裸片,与载体对准因此与逻辑管芯对准。最后,使用高精度堆叠热压键合设备来放置硅桥。

Flip-chip19081305.JPG硅桥连接键合到逻辑裸片上的示例

在随后的模制过🃏程中,裸片仍然会移位,从而损坏TPV和硅桥之间或逻辑裸片和硅桥之间的凸块连接。因此,IMECဣ团队在成型之前和之后进行了专门的电气测试。测试表明,模塑过程不会影响连接的完整性。基于这些结果,可以假设,如果这些裸片在注塑时移位,它们应该是在相同的方向上作整体位移,因而不会破坏连接性。

总结和未来展望

通过这种新颖的ꦑ方法,IMEC团队在ꩲ扇出环境中展示了具有20μm凸块节距的创纪录的芯片到芯片互连密度。在不久的将来,该技术将得到进一步改进,电气和射频行为将以不同的配置进行评估。

所提出的技术对于移动应用🐬尤其具有吸引力,因为它以非常小的形状因子实现了经济有效的WideI / O存储器到逻辑芯片互连。

最终,FO-WLP上的倒装芯片也可能成为异构集成的支持技术,🀅瞄准高性能应🔯用。它可以提供一种在电气高度互连的封装中集成多个裸片的方法,包括高性能计算,存储器和光通信模块。